1. 반도체 제조 과정의 개요

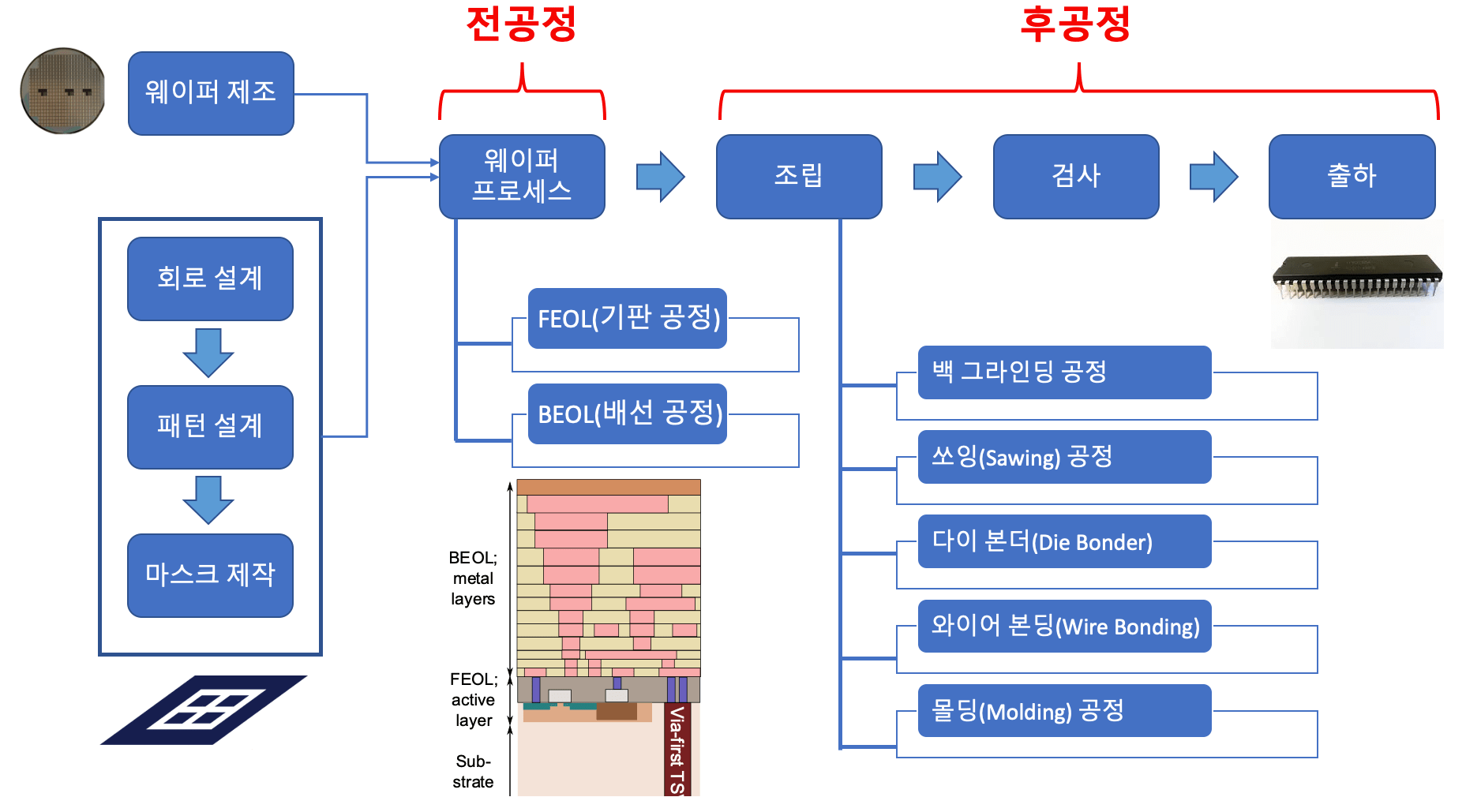

반도체 제조는 전공정과 후공정으로 구분되며, 각 공정은 고도의 정밀성과 첨단 기술이 요구됩니다.

1. 전공정(FEOL, Front-End of Line)

• 목적: 실리콘 웨이퍼에 트랜지스터, 다이오드 등 반도체 소자를 제작.

• 주요 특징: 미세공정 기술을 활용해 소자를 집적하고, 신호 처리 및 저장 기능을 구현.

2. 후공정(BEOL, Back-End of Line)

• 목적: 전공정에서 만들어진 칩을 절단, 패키징하여 최종 반도체 제품으로 완성.

• 주요 특징: 칩 보호와 기기 연결성을 제공하며, 품질 검사를 통해 최종 제품 신뢰성을 확보.

2. 전공정 (Front-End Process) 상세 설명

전공정은 웨이퍼에서 반도체 소자를 형성하는 단계로, 아래 주요 공정으로 구성됩니다.

(1) 웨이퍼 생산

• 원재료: 실리콘(Si) 결정체.

• 제조 과정:

1. Czochralski(CZ) 공정: 실리콘 잉곳(Ingot)을 성장시켜 원기둥 형태로 제작.

2. 잉곳 절단: 다이아몬드 블레이드로 웨이퍼 두께에 맞게 절단.

3. 연마 및 세정: 웨이퍼 표면을 평탄화하고, 오염 물질을 제거.

(2) 웨이퍼 세정

• 필요성: 각 공정 단계에서 불순물이 존재하면 소자의 신뢰성에 영향을 미침.

• 방법: 산성, 알칼리성 용액 및 DI(Deionized) 물을 사용한 화학적 세정.

(3) 산화(Oxidation)

• 목적: 실리콘 표면에 절연층 형성.

• 방법:

• 열 산화(Thermal Oxidation): 고온에서 산소(O₂) 또는 수증기(H₂O)를 사용.

• CVD 산화: 화학적 기상 증착(Chemical Vapor Deposition)으로 박막 형성.

(4) 포토리소그래피(Photolithography)

• 목적: 회로 패턴을 웨이퍼에 형성.

• 과정:

1. 포토레지스트(PR) 코팅.

2. 노광(Exposure): 빛(자외선, EUV)을 이용해 패턴 형성.

3. 현상(Development): 노광된 영역을 용액으로 제거.

4. 패턴 전이: 에칭 과정을 통해 웨이퍼 표면에 회로 패턴 구현.

(5) 에칭(Etching)

• 목적: 불필요한 물질 제거 및 회로 패턴 형성.

• 종류:

• 건식 에칭(Dry Etching): 플라즈마 사용. 미세 공정에서 주로 사용.

• 습식 에칭(Wet Etching): 화학 용액 사용. 대량 생산에 적합.

(6) 증착(Deposition)

• 목적: 반도체 소자와 회로를 보호하거나 연결하기 위한 박막(Thin Film) 형성.

• 종류:

• CVD(Chemical Vapor Deposition): 화학 반응을 이용한 박막 증착.

• PVD(Physical Vapor Deposition): 물리적 기법(스퍼터링, 증발)으로 증착.

(7) 이온 주입(Ion Implantation)

• 목적: 웨이퍼에 전기적 특성을 부여하기 위해 불순물(도핑)을 주입.

• 특징: 이온 가속기를 이용하여 웨이퍼 표면에 이온을 투사.

(8) CMP(Chemical Mechanical Polishing)

• 목적: 표면 평탄화로 다층 배선 공정 준비.

• 특징: 기계적 연마와 화학적 반응을 동시에 사용.

(9) 다층 배선(Multi-Layer Interconnects)

• 목적: 소자와 소자를 연결하기 위해 배선 구조 형성.

• 방법: 메탈 배선을 적층 후 절연층 형성.

3. 후공정 (Back-End Process) 상세 설명

후공정은 전공정에서 제작된 칩을 패키징하고 테스트하는 단계입니다.

(1) 다이 분리(Die Singulation)

• 과정: 웨이퍼를 작은 개별 칩(다이)로 절단.

• 기술: 다이아몬드 톱, 레이저 절단 사용.

(2) 칩 검사(Die Inspection)

• 목적: 불량품 검출 및 분류.

• 방법: 광학 검사 및 전기적 테스트.

(3) 패키징(Packaging)

• 목적: 칩을 외부로부터 보호하고, 전기적 연결을 제공.

• 주요 패키징 기술:

1. DIP(Dual Inline Package): 초기 표준 패키지.

2. QFP(Quad Flat Package): 핀 밀도가 높은 형태.

3. BGA(Ball Grid Array): 볼 형태의 접점 배열.

4. FO-WLP(Fan-Out Wafer Level Packaging): 고성능 및 소형화 가능.

(4) 와이어 본딩(Wire Bonding)

• 목적: 칩과 패키지 간의 전기적 연결.

• 방법: 금(Au), 알루미늄(Al) 와이어 사용.

(5) 플립칩 본딩(Flip-Chip Bonding)

• 특징: 다이를 뒤집어 직접 기판에 연결.

• 장점: 고속 및 고밀도 전기 연결 가능.

(6) 몰딩(Molding)

• 목적: 에폭시 수지로 칩을 감싸 외부 충격 및 환경으로부터 보호.

(7) 최종 테스트(Final Test)

• 목적: 전기적 성능과 신뢰성을 확인.

• 종류:

1. 전기적 테스트.

2. 열 신뢰성 테스트.

3. 스트레스 테스트.

4. 전공정과 후공정 비교

항목 전공정 (FEOL) 후공정 (BEOL)

목적 트랜지스터 및 소자 제작 칩 보호 및 전기적 연결 제공

환경 클린룸 필요, 초미세 공정 필수 상대적으로 덜 정밀하지만 보호 및 연결 중요

주요 공정 웨이퍼 세정, 산화, 에칭, 증착 등 다이 분리, 본딩, 몰딩, 테스트

주요 장비 노광기, 이온 주입기, CMP 장비 본딩기, 몰딩기, 테스트 장비

결과물 웨이퍼 기반 반도체 소자 최종 패키징된 반도체 칩

5. 최신 반도체 트렌드

• EUV 리소그래피: 3nm 이하 공정에 필수적.

• 3D 패키징: TSV(Through-Silicon Via)와 같은 기술 활용.

• AI 검사: 공정 효율성과 품질 관리 향상

https://valuable12.com/entry/반도체-용어-총정리-및-삼성전자-HBM-관련-외부-파운드리-협업

'IT & Tech 정보' 카테고리의 다른 글

| CES 2025: 디테일한 분석과 주요 내용 참가기업 양자컴퓨팅 (0) | 2025.01.02 |

|---|---|

| GPT-4o vs o1 비교 글쓰기, 연산, 코딩, 일정짜기 검색 비교 (0) | 2024.12.31 |

| PMP(Project Management Professional) 자격증 개요, 난이도, 과목, 준비방법, 준비기간, 시험보는 방법, 사전교육 총정리 (0) | 2024.12.18 |

| 텍스트로 자동 동영상 생성 AI, 오픈AI의 ‘소라(Sora)’ 기능 사용법 이용법 구독료 (0) | 2024.12.10 |

| 아이폰 ios 18.1 새로운 기능 총정리 통화녹음 ai 인텔리전스 사진 지우개 (0) | 2024.10.30 |